Suchergebnisse für "risc OR v OR assembly OR language OR programming OR using OR esp32 OR c3 OR and OR qemu"

-

Elektor Digital RISC-V Assembly Language Programming using ESP32-C3 and QEMU (E-book)

With the availability of free and open source C/C++ compilers today, you might wonder why someone would be interested in assembler language. What is so compelling about the RISC-V Instruction Set Architecture (ISA)? How does RISC-V differ from existing architectures? And most importantly, how do we gain experience with the RISC-V without a major investment? Is there affordable hardware available? The availability of the Espressif ESP32-C3 chip provides a way to get hands-on experience with RISC-V. The open sourced QEMU emulator adds a 64-bit experience in RISC-V under Linux. These are just two ways for the student and enthusiast alike to explore RISC-V in this book. The projects in this book are boiled down to the barest essentials to keep the assembly language concepts clear and simple. In this manner you will have “aha!” moments rather than puzzling about something difficult. The focus in this book is about learning how to write RISC-V assembly language code without getting bogged down. As you work your way through this tutorial, you’ll build up small demonstration programs to be run and tested. Often the result is some simple printed messages to prove a concept. Once you’ve mastered these basic concepts, you will be well equipped to apply assembly language in larger projects.

€ 34,95

Mitglieder € 27,96

-

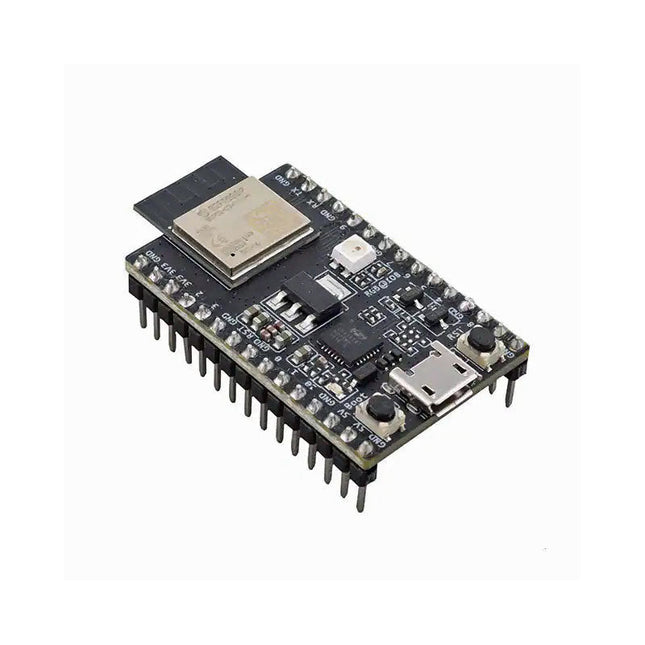

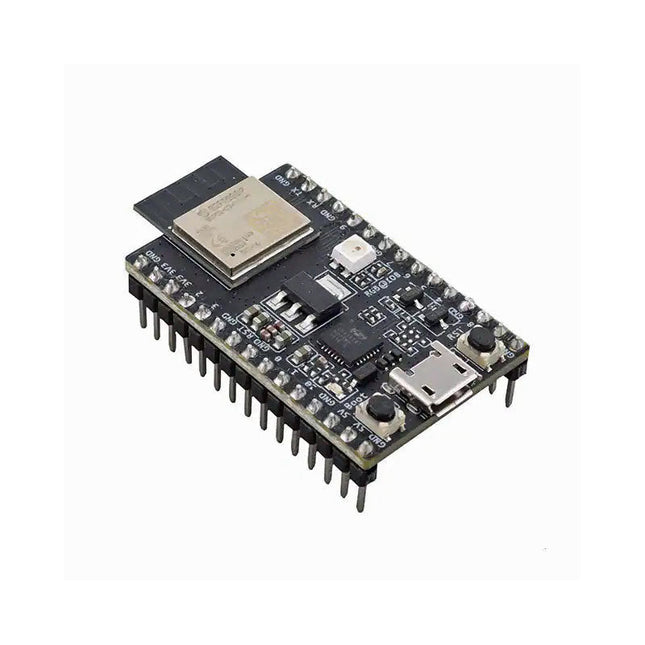

Espressif ESP32-C3-DevKitM-1

ESP32-C3-DevKitM-1 ist ein Einstiegs-Entwicklungsboard, das auf ESP32-C3-MINI-1 basiert, einem Modul, das nach seiner geringen Größe benannt ist. Dieses Board integriert vollständige Wi-Fi- und Bluetooth LE-Funktionen. Die meisten I/O-Pins des ESP32-C3-MINI-1-Moduls sind auf die Stiftleisten auf beiden Seiten des Boards aufgeteilt, um die Anbindung zu erleichtern. Entwickler können Peripheriegeräte entweder mit Jumper-Drähten anschließen oder ESP32-C3-DevKitM-1 auf einem Breadboard montieren. Technische Daten ESP32-C3-MINI-1 ESP32-C3-MINI-1 ist ein Wi-Fi- und Bluetooth-LE-Kombimodul für allgemeine Zwecke, das mit einer PCB-Antenne geliefert wird. Der Kern dieses Moduls ist ESP32-C3FN4, ein Chip mit integriertem Flash von 4 MB. Da der Flash im ESP32-C3FN4-Chip verpackt und nicht in das Modul integriert ist, hat ESP32-C3-MINI-1 eine kleinere Gehäusegröße. 5 V to 3,3 V LDO Leistungsregler, der eine 5-V-Versorgung in einen 3,3-V-Ausgang umwandelt. 5 V Power On LED Leuchtet auf, wenn die USB-Stromversorgung an das Board angeschlossen ist. Pin-Header Alle verfügbaren GPIO-Pins (außer dem SPI-Bus für Flash) sind auf die Stiftleisten auf der Platine ausgebrochen. Einzelheiten finden Sie unter Header-Block. Boot-Button Download-Button. Wenn Sie Boot gedrückt halten und dann Reset drücken, wird der Firmware-Download-Modus zum Herunterladen von Firmware über die serielle Schnittstelle gestartet. Micro-USB Port USB-Interface. Stromversorgung für das Board sowie die Kommunikationsschnittstelle zwischen einem Computer und dem ESP32-C3FN4-Chip. Reset-Button Drücken Sie diese Taste, um das System neu zu starten. USB-to-UART Bridge Ein einzelner USB-UART-Bridge-Chip bietet Übertragungsraten von bis zu 3 Mbit/s. RGB LED Adressierbare RGB-LED, angesteuert von GPIO 8. Downloads ESP32-C3 Datasheet ESP32-C3-MINI-1 Datasheet ESP32-C3-DevKitM-1 Schematic ESP32-C3-DevKitM-1 PCB Layout ESP32-C3-DevKitM-1 Dimensions

€ 19,95€ 7,98

Mitglieder identisch

-

Espressif ESP32-C3-WROOM-02U-N4

ESP32-C3-WROOM-02U ist ein universelles Wi-Fi- und Bluetooth LE-Modul. Die zahlreichen Peripheriegeräte und die hohe Leistung machen das Modul zu einer idealen Wahl für Smart Homes, Industrieautomatisierung, Gesundheitswesen, Unterhaltungselektronik, etc. ESP32-C3-WROOM-02U verfügt über ein externes SPI-Flash und ist mit einem Anschluss für eine externe Antenne ausgestattet. ESP32-C3-WROOM-02U kann bei einer Umgebungstemperatur von -40∼85°C betrieben werden und ist in den ESP32-C3 Chip integriert. ESP32-C3 hat einen 32-Bit RISC-V Single-Core-Prozessor. Er verfügt über eine Vielzahl von Peripheriegeräten wie UART, I²C, I²S, Fernbedienungsperipherie, LED-PWM-Controller, allgemeiner DMA-Controller, TWAI-Controller, USB Serial/JTAG-Controller, Temperatursensor, ADC, etc. Es umfasst auch SPI-, Dual SPI- und Quad SPI-Schnittstellen. Features Flash: 4 MB (Quad SPI) Abmessungen: 18,0 x 20,0 x 3,2 mm Downloads Datasheet

€ 7,95€ 3,18

Mitglieder identisch

-

milkV Milk-V Duo 256M RISC-V Einplatinencomputer

Der Milk-V Duo 256M ist eine ultrakompakte Embedded-Entwicklungsplattform basierend auf dem SG2002-Chip. Es kann Linux und RTOS ausführen und bietet eine zuverlässige, kostengünstige und leistungsstarke Plattform für Profis, industrielle ODMs, AIoT-Enthusiasten, Heimwerker und Entwickler. Dieses Board ist eine aktualisierte Version von Duo mit einer Speichererweiterung auf 256 TMB und eignet sich für Anwendungen, die größere Speicherkapazitäten erfordern. Der SG2002 erhöht die Rechenleistung auf 1,0 TOPS @ INT8. Es ermöglicht den nahtlosen Wechsel zwischen RISC-V/ARM-Architekturen und unterstützt den gleichzeitigen Betrieb dualer Systeme. Darüber hinaus umfasst es eine Reihe umfangreicher GPIO-Schnittstellen wie SPI und UART, die für eine breite Palette von Hardwareentwicklungen im Bereich intelligenter Edge-Überwachung geeignet sind, darunter IP-Kameras, intelligente Türspionschlösser, visuelle Türklingeln und mehr. SG2002 ist ein leistungsstarker Chip mit geringem Stromverbrauch, der für verschiedene Produktbereiche wie intelligente IP-Überwachungskameras, intelligente Türschlösser, visuelle Türklingeln und Heimintelligenz entwickelt wurde. Es integriert H.264-Videokomprimierung und -Dekodierung, H.265-Videokomprimierungskodierung und ISP-Funktionen. Es unterstützt mehrere Bildverbesserungs- und Korrekturalgorithmen wie HDR Wide Dynamic Range, 3D-Rauschunterdrückung, Antibeschlag und Objektivverzerrungskorrektur und bietet Kunden eine professionelle Videobildqualität. Der Chip enthält außerdem eine selbst entwickelte TPU, die 1,0 TOPS Rechenleistung bei 8-Bit-Integer-Operationen liefert. Die speziell entwickelte TPU-Planungs-Engine sorgt effizient für einen Datenfluss mit hoher Bandbreite für alle Kerne der Tensor-Verarbeitungseinheit. Darüber hinaus bietet es Benutzern einen leistungsstarken Deep-Learning-Modell-Compiler und ein Software-SDK-Entwicklungskit. Führende Deep-Learning-Frameworks wie Caffe und Tensorflow können problemlos auf die Plattform portiert werden. Darüber hinaus umfasst es Sicherheitsstart, sichere Updates und Verschlüsselung und bietet eine Reihe von Sicherheitslösungen von der Entwicklung über die Massenproduktion bis hin zu Produktanwendungen. Der Chip integriert ein 8-Bit-MCU-Subsystem und ersetzt die typische externe MCU, um Kosteneinsparungs- und Energieeffizienzziele zu erreichen. Technische Daten SoC SG2002 RISC-V CPU C906 @ 1 Ghz + C906 @ 700 MHz Arm CPU 1x Cortex-A53 @ 1 GHz MCU 8051 @ 6 KB SRAM Speicher 256 MB SIP-DRAM TPU 1,0 TOPS @ INT8 Speicher 1x microSD-Anschluss oder 1x SD NAND an Bord USB 1x USB-C für Strom und Daten, USB-Pads verfügbar CSI 1x 16P FPC-Anschluss (MIPI CSI 2-spurig) Sensorunterstützung 5 M bei 30 fps Ethernet 100 Mbit/s Ethernet mit PHY Audio Über GPIO-Pads GPIO Bis zu 26x GPIO-Pads Stromversorgung 5 V/1 A OS-Unterstützung Linux, RTOS Abmessungen 21 x 51 mm Downloads Documentation GitHub

€ 32,95€ 13,18

Mitglieder identisch

-

Elektor Digital Assembly Language Essentials (E-book)

A Guide to Powerful Programming for Embedded Systems You must be a well-rounded professional to excel in the ever-evolving, rapidly developing embedded design and programming industry. Simply put, when it comes to electronics design and programming, the more topics you can master, the more you’ll flourish at your workplace and at your personal workbench. This shouldn’t be a surprise, as the line between the skills of a hardware engineer and software engineer is blurring. The former should have a good grasp of programming in order to build efficient systems. The latter should understand the details of the design (whether it’s a physical or virtual application) for which he or she is writing code. Thus, to be successful, a modern professional electronics engineer must have a solid grasp of both hardware design and programming. Assembly Language Essentials is a matter-of-fact guide to Assembly that will introduce you to the most fundamental programming language of a processor. Unlike other resources about Assembly that focus exclusively on specific processors and platforms, this book uses the architecture of a fictional processor with its own hardware and instruction set. This enables you to consider the importance of Assembly language without having to deal with predetermined hardware or architectural restrictions. You’ll immediately find this thorough introduction to Assembly to be a valuable resource, whether you know nothing about the language or you have used it before. The only prerequisite is that you have a working knowledge of at least one higher-level programming language, such as C or Java. Assembly Language Essentials is an indispensible resource for electronics engineering professionals, academics, and advanced students looking to enhance their programming skills. The book provides the following, and more: An introduction to Assembly language and its functionality Significant definitions associated with Assembly language, as well as essential terminology pertaining to higher-level programming languages and computer architecture Important algorithms that may be built into high-level languages, but must be done the “hard way” in Assembly language — multiplication, division, and polynomial evaluation A presentation of Interrupt Service Routines with examples A free, downloadable Assembler program for experimenting with Assembly

€ 29,95

Mitglieder € 23,96

-

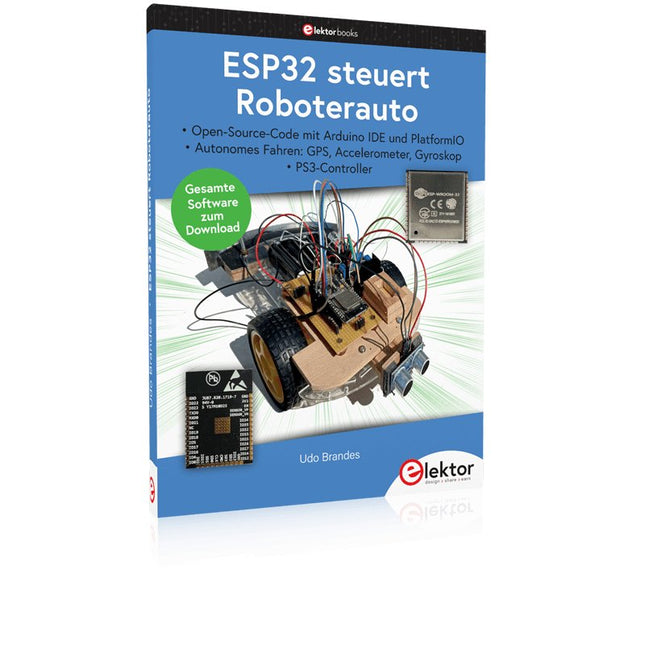

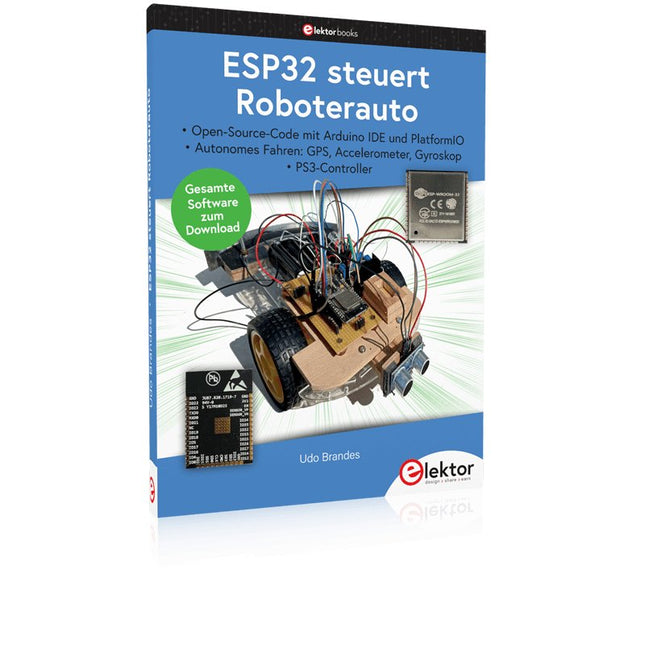

Elektor Publishing ESP32 steuert Roboterauto

Open-Source-Code mit Arduino IDE und PlatformIO Autonomes Fahren: GPS, Accelerometer, Gyroskop PS3-Controller Mikrocontroller wie der Arduino und Einplatinenrechner wie der Raspberry Pi haben sich zu beliebten Komponenten entwickelt. Dritter im Bunde ist der ESP32 der Firma Espressif. Mikrocontroller dieser Baureihe zeichnen sich durch eine Vielzahl implementierter Funktionen aus, die bei einem Arduino konventioneller Prägung mit einem Atmel-AVR-Mikrocontroller erst mit weiterer Hardware möglich sind. Prominentes Beispiel sind hier die WiFi- und Bluetooth-Funktionalitäten. Gegenüber einem Raspberry Pi zeichnen sie sich durch einen deutlich geringeren Preis aus. Allgemeine Informationen für die Realisierung eines Roboterauto-Projekts mit dem ESP32 sind leicht zu finden. Dabei handelt es sich aber oft nur um Ausführungen zu einem Teilaspekt, ohne inhaltliche oder funktionale Abstimmung. So ist nicht nur die Beschaffung der benötigten Informationen mühselig und zeitaufwändig, sie kann auch außerordentlich fehlerträchtig sein. Ansatzpunkt dieses Buches ist, diese Lücke zu schließen. Es geht auf verschiedene Möglichkeiten eines Chassis ein, vermittelt nötige Kenntnisse und führt schrittweise von einer einfachen Motorsteuerung zu einem komplexen sensor- und sprachgesteuerten Roboterauto. Hacks rund um GPS und eine PlayStation 3 runden die Sache ab. Inhalt Bei der Reihenfolge der Kapitel wurde versucht – beginnend bei der Darstellung von grundlegenden Informationen – über die Lösung einfacher Aufgaben zu etwas anspruchsvolleren Techniken zu führen. Der Mikrocontroller ESP32 Die Software erstellen Die Stromversorgung Rund um die Hardware Das Chassis Der Gleichstrommotor Kabellose Steuerung über WiFi Mit Sensoren Hindernisse erkennen Eine eigene Roboterauto-App Servo und Lichtsensor GPS Accelerometer / Gyroskop PS3-Controller Roboterauto-App Hinweis zur Software Die Dateien haben das Suffix (.cpp). Grund ist die Entwicklung mit PlatformIO. Mit Copy & Paste sollten sie auch in der Arduino-IDE verwendet werden können.

€ 39,80

Mitglieder identisch

-

Espressif ESP32-WROOM-32D

Der ESP32-WROOM-32 misst nur 25,2 x 18 mm und enthält den ESP32-SoC, den Flash-Speicher, präzise diskrete Komponenten und eine PCB-Antenne, um eine hervorragende HF-Leistung in Anwendungen mit begrenztem Platzangebot zu bieten. ESP32-WROOM-32 ist ein leistungsstarkes, generisches Wi-Fi + BT + BLE-MCU-Modul, das auf eine Vielzahl von Anwendungen abzielt, von Sensornetzwerken mit geringem Stromverbrauch bis hin zu anspruchsvollsten Aufgaben wie Sprachkodierung, Musik-Streaming und MP3-Dekodierung. Das Herzstück dieses Moduls ist der ESP32-D0WDQ6-Chip. Der eingebettete Chip ist skalierbar und anpassungsfähig. Es gibt zwei CPU-Kerne, die einzeln angesteuert werden können, und die Taktfrequenz ist von 80 MHz bis 240 MHz einstellbar. Der Benutzer kann die CPU auch ausschalten und den stromsparenden Coprozessor nutzen, um die Peripheriegeräte ständig auf Änderungen oder Überschreitungen von Schwellenwerten zu überwachen. ESP32 integriert eine Vielzahl von Peripheriegeräten, die von kapazitiven Berührungssensoren, Hall-Sensoren, SD-Kartenschnittstelle, Ethernet, Hochgeschwindigkeits-SPI, UART, I²S und I²C reichen. Die Integration von Bluetooth, Bluetooth LE und Wi-Fi sorgt dafür, dass ein breites Anwendungsspektrum angesprochen werden kann und das Modul zukunftssicher ist. Die Verwendung von Wi-Fi ermöglicht eine große physische Reichweite und eine direkte Verbindung zum Internet über einen Wi-Fi-Router, während die Verwendung von Bluetooth es dem Benutzer ermöglicht, bequem eine Verbindung zum Telefon herzustellen oder Niedrigenergie-Beacons zur Erkennung auszusenden. Der Ruhestrom des ESP32-Chips beträgt weniger als 5 µA und eignet sich daher für batteriebetriebene und tragbare Elektronikanwendungen. ESP32 unterstützt eine Datenrate von bis zu 150 Mbit/s und eine Ausgangsleistung von 20,5 dBm an der Antenne, um die größtmögliche physikalische Reichweite zu gewährleisten. Daher bietet der Chip branchenführende Spezifikationen und die beste Leistung für elektronische Integration, Reichweite, Stromverbrauch und Konnektivität. Downloads Datasheet

€ 9,95€ 3,98

Mitglieder identisch

-

Espressif ESP32-S2-WROVER

Das Herzstück dieses Moduls ist ESP32-S2, eine Xtensa® 32-Bit-LX7-CPU, die mit bis zu 240 MHz arbeitet. Der Chip verfügt über einen Co-Prozessor mit geringem Stromverbrauch, der anstelle der CPU verwendet werden kann, um Strom zu sparen und gleichzeitig Aufgaben auszuführen, die nicht viel Rechenleistung erfordern, wie beispielsweise die Überwachung von Peripheriegeräten. ESP32-S2 integriert eine Vielzahl von Peripheriegeräten, darunter SPI, I²S, UART, I²C, LED-PWM, TWAITM, LCD, Kameraschnittstelle, ADC, DAC, Berührungssensor, Temperatursensor sowie bis zu 43 GPIOs. Es verfügt außerdem über eine Full-Speed-USB-On-The-Go-Schnittstelle (OTG), um die USB-Kommunikation zu ermöglichen. Merkmale MCU ESP32-S2 eingebetteter Xtensa®-Single-Core-32-Bit-LX7-Mikroprozessor, bis zu 240 MHz 128 KB ROM 320 KB SRAM 16 KB SRAM im RTC W-lan 802.11 b/g/n Bitrate: 802.11n bis zu 150 Mbit/s A-MPDU- und A-MSDU-Aggregation Unterstützung für 0,4 µs Schutzintervall Mittenfrequenzbereich des Betriebskanals: 2412 ~ 2484 MHz Hardware Schnittstellen: GPIO, SPI, LCD, UART, I²C, I²S, Kameraschnittstelle, IR, Impulszähler, LED-PWM, TWAI (kompatibel mit ISO 11898-1), USB OTG 1.1, ADC, DAC, Berührungssensor, Temperatursensor 40-MHz-Quarzoszillator 4 MB SPI-Flash Betriebsspannung/Stromversorgung: 3,0 ~ 3,6 V Betriebstemperaturbereich: –40 ~ 85 °C Abmessungen: 18 × 31 × 3,3 mm Anwendungen Allgemeiner IoT-Sensor-Hub mit geringem Stromverbrauch Generische IoT-Datenlogger mit geringem Stromverbrauch Kameras für Video-Streaming Over-the-Top-Geräte (OTT). USB-Geräte Spracherkennung Bilderkennung Mesh-Netzwerk Heimautomatisierung Smart-Home-Systemsteuerung Intelligentes Gebäude Industrielle Automatisierung Intelligente Landwirtschaft Audioanwendungen Anwendungen im Gesundheitswesen Wi-Fi-fähiges Spielzeug Tragbare Elektronik Einzelhandels- und Gastronomieanwendungen Intelligente POS-Geräte

€ 7,95€ 3,18

Mitglieder identisch

-

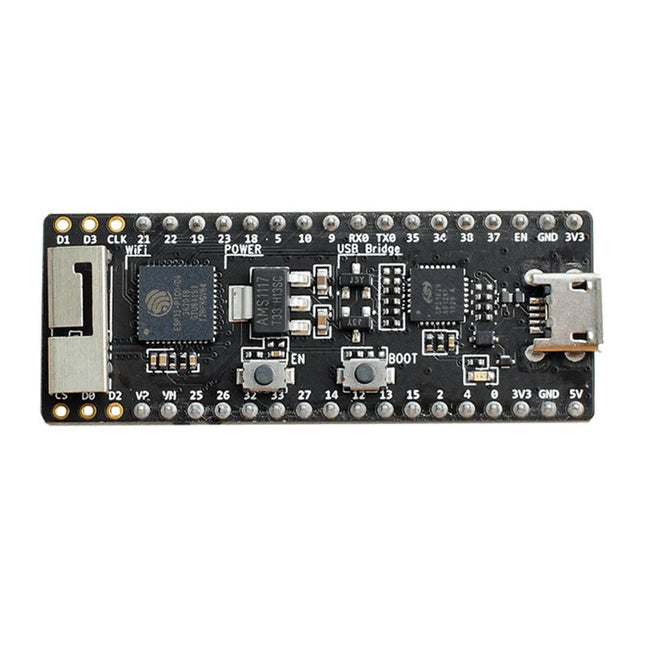

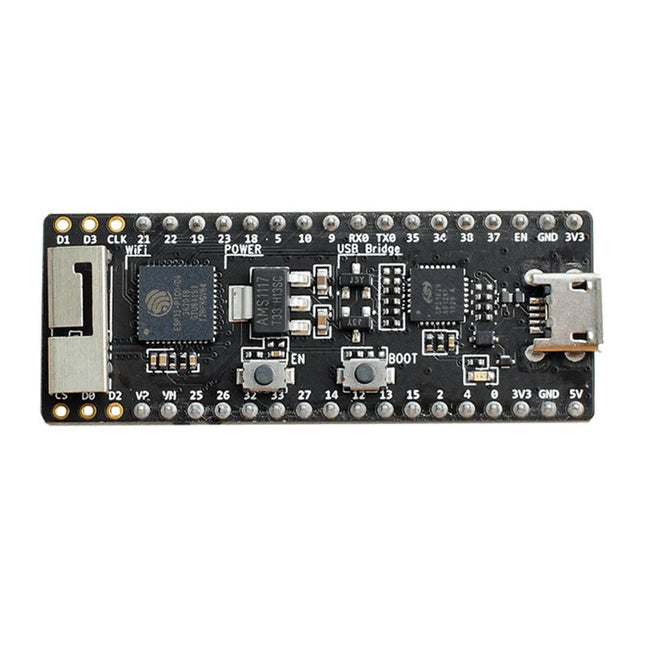

Espressif ESP32-PICO-Kit

Das ESP32-PICO-KIT passt in ein Mini-Breadboard. Es ist voll funktionsfähig mit der minimalen Anzahl von diskreten Komponenten, während es alle ESP32-Pins freilegt. Features Eine vollständige und aktuelle Dokumentation ist verfügbar. Alle vorgestellten Anweisungen und Befehle funktionieren wie beschrieben. Zusätzliche Informationen und Hardware-Dokumentation sind ebenfalls reichlich vorhanden. Applikationen für das ESP32-PICO-KIT können auf Windows, Linux oder Mac entwickelt werden. Zwei Kerne und ein Funkgerät Wie der ESP8266 hat der ESP32 Wi-Fi, aber zusätzlich Bluetooth. Außerdem hat er zwei 32-Bit-Kerne im Inneren, die ihn extrem leistungsfähig machen und alle Ports und Schnittstellen bieten, die dem ESP8266 fehlen.Vereinfachend könnte man sagen, dass der ESP8266 ein Wi-Fi-Controller ist, der einige I/Os bietet, während der ESP32 ein vollwertiger Controller ist, der auch Wi-Fi hat. ESP32-Peripheriegeräte Der ESP32 verfügt über einen ADC & DAC, eine Touch-Sensor-Schaltung, einen SD/SDIO/MMC-Host-Controller, einen SDIO/SPI-Slave-Controller, einen EMAC, PWM zur Steuerung von LEDs und Motoren, UART, SPI, I²C, I²S, Infrarot-Fernbedienung und natürlich GPIO. ESP32-PICO-KIT Entwicklungsboard Das ESP32-PICO-D4 ist ein System-on-Chip (SoC), das einen ESP32-Chip zusammen mit einem 4 MB SPI-Flash-Speicher in einem winzigen 7 x 7 mm Gehäuse integriert. Das ESP32-PICO-KIT ist ein Breakout-Board für diesen SoC mit einem integrierten USB-seriell-Wandler für einfache Programmierung und Debugging. Neben dem Board benötigen Sie eine Programmier-Toolchain. Eine vollständige, aktuelle Dokumentation von Espressif finden Sie auf der Read the Docs-Website.Alle vorgestellten Anleitungen und Befehle funktionieren wie beschrieben.Zusätzliche Informationen und Hardware-Dokumentationen sind ebenfalls reichlich vorhanden. Applikationen für das ESP32-PICO-KIT können auf Windows, Linux oder Mac entwickelt werde

€ 19,95€ 7,98

Mitglieder identisch

-

Elektor Academy Pro ESP32 by Example (Lernkurs)

Vollständiger ESP32-Mikrocontroller-Lernkurs mit speziell entwickelter MCU-Erweiterungsplatine, praxisorientierten Projekten und einem umfassenden Online-Guide – ideal, um Hardware, Programmierung und Konnektivität Schritt für Schritt zu erlernen. Praktische Einführung in eingebettete Systeme mit dem ESP32 Dieser Kurs richtet sich an Einsteiger in die Welt der eingebetteten Systeme, die einen strukturierten, beispielorientierten Einstieg suchen. Falls Sie sich bereits mit allgemeiner Elektronik oder Arduino-basierten Materialien beschäftigt haben, diese aber als zu allgemein oder zu wenig praxisnah empfunden haben, bietet dieser Kurs eine fokussiertere Alternative. Mit dem "ESP32 by Example Kit" (EEK) – einem kompakten und kostengünstigen Komponentensatz mit LEDs, Sensoren, einem OLED-Display und einem Bewegungsprozessor – arbeiten Sie während des gesamten Kurses mit einem einheitlichen Hardware-Setup. Nach dem Zusammenbau bleibt das EEK weitgehend unverändert, sodass Sie sich ganz auf das Lernen und Experimentieren konzentrieren können, ohne ständig neu konfigurieren zu müssen. Themen: Verstehen und Programmieren des ESP32-Mikrocontrollers Programmieren und Ausführen von Code mit der Arduino IIDE Erkunden von cyber-physischen Systemen, abschließend zur grundlegenden Drohnensteuerung Vorkenntnisse in Arduino oder Embedded-Entwicklung sind nicht erforderlich. Jeder Abschnitt enthält praktische Beispiele und Miniprojekte, die die wichtigsten Konzepte festigen und zu einer tiefergehenden Auseinandersetzung anregen. Am Ende des Kurses können Sie die Beispiele des Buches nicht nur nachvollziehen, sondern auch mit eigenen Ideen und Anwendungen erweitern. Ob Sie sich für Embedded-Programmierung, interaktive Systeme oder die Grundlagen der Drohnensteuerung interessieren – dieser Kurs bietet einen klaren und praxisorientierten Einstieg. Was Sie lernen werden Eingebettete Programmierung mit dem ESP32 mithilfe der Arduino IDE Echtzeit-Sensoreingabe und -steuerung über Tasten, LEDs und Displays Gestenbasierte Interaktion mit dem Bewegungssensor MPU6050 Integration von Bluetooth-Gamepads und Drohnensteuerungssimulation WLAN- und UDP-Netzwerke, lokale Webserver und NTP MQTT-Kommunikation mit Cloud-Plattformen wie AWS und Arduino IoT Aufbau und Bereitstellung voll funktionsfähiger IoT-Systeme Perfekt für Studierende und Autodidakten, die sich mit eingebetteten Systemen beschäftigen Bastler und IoT-Begeisterte, die ihre Hardwarekenntnisse verbessern möchten Lehrkräfte und Dozenten, die nach sofort einsetzbarem Unterrichtsmaterial suchen Entwickler, die über die Grundlagen von Raspberry Pi oder Arduino hinausgehen möchten Support, wenn Sie ihn brauchen Zugang zu Kursleitern über die Elektor Academy Hilfreiche Community-Foren und wichtige Dokumentation Was ist in der Box (Kurs)? Neues 384-seitiges Buch: "ESP32 by Example" (Wert: 45 €) Elektor ESP32 by Example Kit (EEK): Mikrocontroller-Erweiterungsplatine mit 6 LEDs und 6 Tasten + OLED-Display, MPU6050 3-Achsen Beschleunigungsmesser und Gyroskop-Modul (Wert: 40 €) Adafruit HUZZAH32 – ESP32 Feather MCU Board (Wert: 30 €) ESP32 Cheap Yellow Display Board (Wert: 25 €) DHT11 Feuchtigkeitssensor & Temperatursensor Breadboard Jumperkabel USB-C-Kabel Zugang zum vollständigen Kurs auf der Elektor Academy Pro Lernplattform Lehrvideos Herunterladbare Arduino-Projektdateien für jedes Modul Lernmaterial (dieser Box) ▶ Klicken Sie hier zum Öffnen Module 1 – Getting Started with the ESP32 & EEK Module 2 – Digital Output – LEDs and GPIO Module 3 – Switches and Input Handling Module 4 – EEK and PWM Module 5 – OLED and Display Output Module 6 – Motion Sensing with the MPU6050 Module 7 – Capstone Project (EEK in Action) Module 8 – WiFi and Web Control with ESP32 Module 9 – Cloud Concepts using EEK Module 10 – Hands-on: Arduino IoT Cloud and EEK Module 11 – BlueTooth and EEK GamePad Integration Module 12 – Why Drones? Module 13 – Drone Simulator Concepts Module 14 – Simple Drone Flight Control Module 15 – Real-Time Drone Flight Control Module 16 – Drone Control Mini-Projects Module 17 – Middleware and Python Scripting Module 18 – Python Applications for Drone Control Module 19 – Capstone EEK Control Project and Presentation Über den Autor Dr. Jim Solderitsch ist Dozent, Softwarearchitekt, Systementwickler und Cybersicherheitsforscher mit Schwerpunkt auf cyber-physischen Systemen. Derzeit ist er als Lehrbeauftragter für Informatik an der Villanova University in Pennsylvania tätig. Was ist Elektor Academy Pro? Elektor Academy Pro bietet maßgeschneiderte Lernlösungen für Fachkräfte, Ingenieurteams und technische Experten in der Elektronik- und Embedded-Systems-Branche. Sie unterstützt Einzelpersonen und Organisationen dabei, ihr praktisches Know-how zu vertiefen, ihre Skills gezielt auszubauen und dank hochwertiger Inhalte und praxisnaher Tools stets einen Schritt voraus zu sein. Von realen Projekten und spezialisierten Kursen bis hin zu fundierten technischen Insights – Elektor versetzt Ingenieure in die Lage, aktuelle Herausforderungen der Branche erfolgreich zu meistern. Unser Bildungsportfolio umfasst Academy-Bücher, Pro-Boxen, Webinare, Konferenzen und B2B-Fachmagazine – alles mit Blick auf praxisnahe Weiterbildung und berufliches Wachstum. Ob Ingenieur, F&E-Spezialist oder technischer Entscheider: Elektor Academy Pro schlägt die Brücke zwischen Theorie und Praxis – und hilft Ihnen, neue Technologien zu beherrschen und Innovationen in Ihrem Unternehmen gezielt voranzutreiben.

€ 269,00€ 219,00

Mitglieder identisch

-

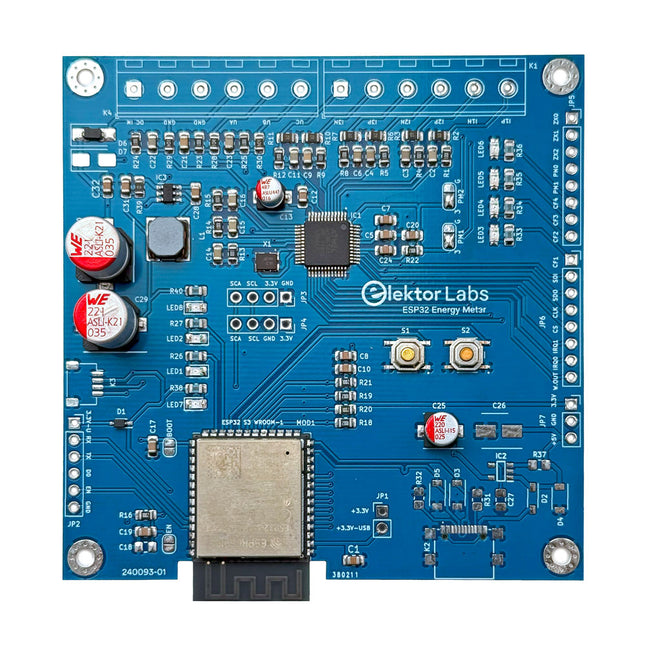

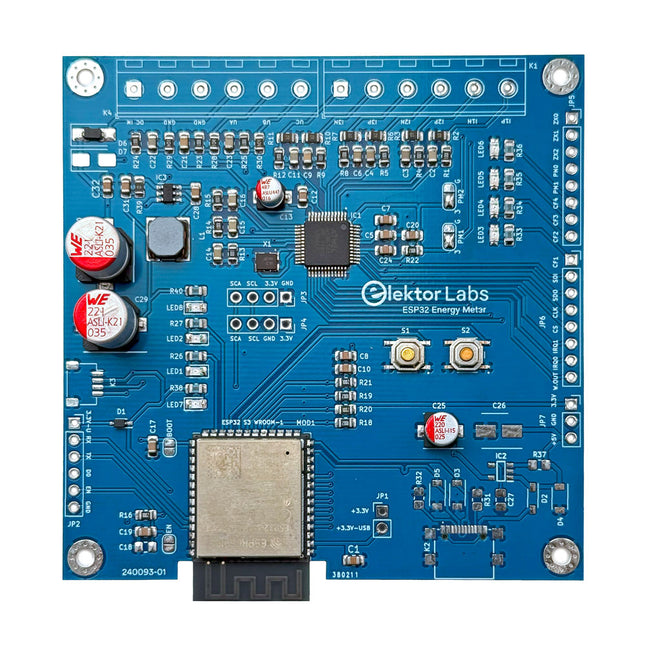

Elektor Labs Elektor ESP32-Energiemessgerät

Das Elektor ESP32-Energiemessgerät wurde für die Echtzeit-Energieüberwachung und die Smart Home-Integration entwickelt. Angetrieben durch den ESP32-S3 Mikrocontroller bietet es robuste Leistung mit modularen und skalierbaren Funktionen. Das Gerät verwendet einen 220 V-auf-12 V-Abwärtstransformator zur Spannungsabtastung, der eine galvanische Trennung und Sicherheit gewährleistet. Sein kompaktes Platinenlayout umfasst Schraubklemmenblöcke für sichere Verbindungen, einen Qwiic-Anschluss für zusätzliche Sensoren und einen Programmier-Header für die direkte ESP32-S3-Konfiguration. Der Energiezähler ist mit einphasigen und dreiphasigen Systemen kompatibel und somit für verschiedene Anwendungen anpassbar. Das Energiemessgerät ist einfach einzurichten und lässt sich in Home Assistant integrieren. Er bietet Echtzeitüberwachung, Verlaufsanalysen und Automatisierungsfunktionen. Es liefert genaue Messungen von Spannung, Strom und Leistung und ist damit ein wertvolles Werkzeug für das Energiemanagement in Haushalten und Unternehmen. Features Umfassende Energieüberwachung: Erhalten Sie detaillierte Einblicke in Ihren Energieverbrauch für eine intelligentere Verwaltung. Anpassbare Software: Passen Sie die Funktionalität an Ihre Bedürfnisse an, indem Sie eigene Sensoren programmieren und integrieren. Smart Home Ready: Kompatibel mit ESPHome, Home Assistant und MQTT für vollständige Smart Home-Integration. Sicher & Flexibles Design: Funktioniert mit einem 220 V-zu-12 V-Abwärtstransformator und verfügt über eine vormontierte SMD-Platine. Schnellstart: Enthält einen Stromwandlersensor und Zugang zu kostenlosen Einrichtungsressourcen. Technische Daten Mikrocontroller ESP32-S3-WROOM-1-N8R2 Energiemess-IC ATM90E32AS Statusanzeigen 4x LEDs zur Anzeige des Stromverbrauchs2x programmierbare LEDs für benutzerdefinierte Statusbenachrichtigungen Benutzereingabe 2x Drucktasten zur Benutzersteuerung Ausgabe anzeigen I²C-OLED-Display zur Echtzeit-Anzeige des Stromverbrauchs Eingangsspannung 110/220 V AC (über Abwärtstransformator) Eingangsleistung 12 V (über Abwärtstransformator oder DC-Eingang) Klemmstromsensor YHDC SCT013-000 (100 A/50 mA) im Lieferumfang enthalten Smart Home-Integration ESPHome, Home Assistant und MQTT für nahtlose Konnektivität Konnektivität Header für die Programmierung, Qwiic für Sensorerweiterung Anwendungen Unterstützt einphasige und dreiphasige Energieüberwachungssysteme Abmessungen 79,5 x 79,5 mm Lieferumfang 1x Teilbestückte Platine (SMD-Bauteile sind vormontiert) 2x Schraubklemmenblock-Anschlüsse (nicht montiert) 1x YHDC SCT013-000 Stromwandler Erforderlich Netztransformator nicht enthalten Downloads Datasheet (ESP32-S3-WROOM-1) Datasheet (ATM90E32AS) Datasheet (SCT013-000) Frequently Asked Questions (FAQ) Vom Prototyp zum fertigen Produkt Was als innovatives Projekt zur Entwicklung eines zuverlässigen und benutzerfreundlichen Energiemessgeräts mithilfe des ESP32-S3-Mikrocontrollers begann, hat sich zu einem robusten Produkt entwickelt. Ursprünglich als Open-Source-Projekt entwickelt, zielte das Gerät darauf ab, eine präzise Energieüberwachung, Smart-Home-Integration und mehr zu ermöglichen. Durch sorgfältige Hardware- und Firmware-Entwicklung ist das Energiemessgerät heute eine kompakte, vielseitige Lösung für das Energiemanagement.

€ 79,95€ 64,95

Mitglieder identisch

-

Espressif ESP32-S2-WROOM

Das Herzstück dieses Moduls ist ESP32-S2, eine Xtensa® 32-Bit-LX7-CPU, die mit bis zu 240 MHz arbeitet. Der Chip verfügt über einen Co-Prozessor mit geringem Stromverbrauch, der anstelle der CPU verwendet werden kann, um Strom zu sparen und gleichzeitig Aufgaben auszuführen, die nicht viel Rechenleistung erfordern, wie beispielsweise die Überwachung von Peripheriegeräten. ESP32-S2 integriert eine Vielzahl von Peripheriegeräten, darunter SPI, I²S, UART, I²C, LED-PWM, TWAITM, LCD, Kameraschnittstelle, ADC, DAC, Berührungssensor, Temperatursensor sowie bis zu 43 GPIOs. Es verfügt außerdem über eine Full-Speed-USB-On-The-Go-Schnittstelle (OTG), um die USB-Kommunikation zu ermöglichen. Merkmale MCU ESP32-S2 eingebetteter Xtensa®-Single-Core-32-Bit-LX7-Mikroprozessor, bis zu 240 MHz 128 KB ROM 320 KB SRAM 16 KB SRAM im RTC W-lan 802.11 b/g/n Bitrate: 802.11n bis zu 150 Mbit/s A-MPDU- und A-MSDU-Aggregation Unterstützung für 0,4 µs Schutzintervall Mittenfrequenzbereich des Betriebskanals: 2412 ~ 2484 MHz Hardware Schnittstellen: GPIO, SPI, LCD, UART, I²C, I²S, Kameraschnittstelle, IR, Impulszähler, LED-PWM, TWAI (kompatibel mit ISO 11898-1), USB OTG 1.1, ADC, DAC, Berührungssensor, Temperatursensor 40-MHz-Quarzoszillator 4 MB SPI-Flash Betriebsspannung/Stromversorgung: 3,0 ~ 3,6 V Betriebstemperaturbereich: –40 ~ 85 °C Abmessungen: 18 × 31 × 3,3 mm Anwendungen Allgemeiner IoT-Sensor-Hub mit geringem Stromverbrauch Generische IoT-Datenlogger mit geringem Stromverbrauch Kameras für Video-Streaming Over-the-Top-Geräte (OTT). USB-Geräte Spracherkennung Bilderkennung Mesh-Netzwerk Heimautomatisierung Smart-Home-Systemsteuerung Intelligentes Gebäude Industrielle Automatisierung Intelligente Landwirtschaft Audioanwendungen Anwendungen im Gesundheitswesen Wi-Fi-fähiges Spielzeug Tragbare Elektronik Einzelhandels- und Gastronomieanwendungen Intelligente POS-Geräte

€ 6,95€ 2,78

Mitglieder identisch